Verilog学习笔记简单功能实现(八)...............同步FIFO

Part 1,功能定义:

用16*8 RAM实现一个同步先进先出(FIFO)队列设计。由写使能端控制该数据流的写入FIFO,并由读使能控制FIFO中数据的读出。写入和读出的操作(高电平有效)由时钟的上升沿触发。当FIFO的数据满和空的时候分别设置相应的高电平加以指示。FIFO是英文First In First Out 的缩写,是一种先进先出的数据缓存器,它与普通存储器的区别是没有外部读写地址线,这样使用起来非常简单,但缺点就是只能顺序写入数据,顺序的读出数据,其数据地址由内部读写指针自动加1完成,不能像普通存储器那样可以由地址线决定读取或写入某个指定的地址。

所谓同步FIFO是指读时钟和写时钟采用同一个时钟。同时,异步FIFO就是指读写时钟不一致。

Part 2.顶层信号定义:

|

信号名称 |

I/O |

功能描述 |

源/目标 |

备注 |

|

Rst |

In |

全局复位(低有效) |

管脚 |

|

|

Clk |

In |

全局时钟 |

管脚 |

频率10Mhz;占空比:50% |

|

W_en |

In |

高有效写使能 |

管脚 |

|

|

R_en |

In |

高有效读使能 |

管脚 |

|

|

Data_in[7:0] |

In |

数据输入端 |

管脚 |

|

|

Data_out[7:0] |

Out |

数据输出端 |

管脚 |

|

|

Empty |

Out |

空指示信号 |

管脚 |

为高时表示fifo空 |

|

Full |

Out |

满指示信号 |

管脚 |

为高时表示fifo满 |

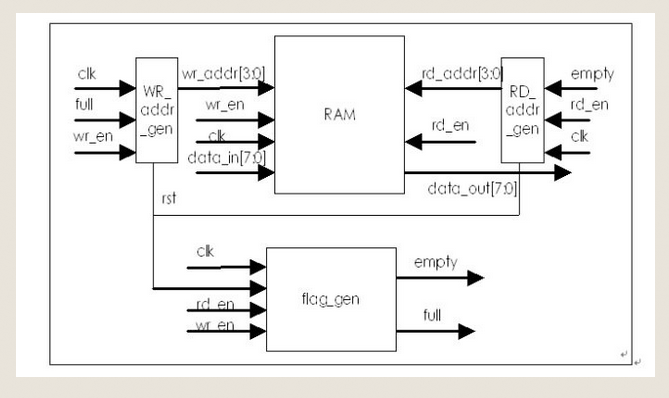

Part 3.顶层模块即划分:

该同步fifo可划分为如下四个模块,如图所示:

①存储器模块(RAM) ——用于存放及输出数据;

②读地址模块(r_addr) ——用于读地址的产生;

③写地址模块(w_addr)——用于写地址的产生

④标志模块(flag_gen) ---- 用于产生FIFO当前空满状态。

Part 4.RAM块:

RAM块的源码

本设计中采用16*8的双扣RAM,以循环读写的方式实现。

根据r_addr模块产生的读地址在,读使能(ren==1)时,将r_addr[4:0]地址中的对应单元的数据在时钟上升沿到来时,读出到data_out[7:0]中;

根据w_addr模块产生的写地址,在写实能(wen==1)时,在时钟沿的上升沿到来时,将data_in[7:0]中的数据写入到w_addr[4:0]地址对应的单元。

//16*8 RAM define (七个端口)

module RAM(clk,ren,wen,r_addr,w_addr,data_in,data_out);

input clk,ren,wen;

input [:]r_addr,w_addr;

input [:]data_in;

output [:]data_out;

reg [:]data_out;

reg [:]fifo[:];

always @(posedge clk)

begin

if(ren==)

begin data_out<=fifo[r_addr]; end

end

always @(posedge clk)

begin

if(wen==)

begin fifo[w_addr]<=data_in; end

end

endmodule

Part 5.r_addr产生块:

该模块用于产生FIFO读数据时所用的地址。由于16个RAM单元可以用4位地址线寻址。本模块用5位计数器(rd_addr[4:0])实现读地址的产生。

在复位时(rst=0),读地址值为0。

如果FIFO未空(~empty)且有读使能(r_en)有效,则r_addr[4:0]加1;否则不变。

//read address genaration

module r_addr_gen(clk,rst,ren,r_addr,empty);

input clk,rst,ren,empty;

output [:]r_addr;

reg [:]r_addr;

always @(posedge clk) //negedge rst can be here to make it asynchronous

begin

if (!rst) begin r_addr<='b00000; end

else if(ren==&&empty==) begin r_addr<=r_addr+;end

else begin r_addr<='b00000; end

end

endmodule

Part 6.w_addr产生块:

该模块用于产生FIFO写数据时所用的地址。由于16个RAM单元可以用4位地址线寻址。

在复位时(rst=0),写地址值为0。

如果FIFO未满(~full)且有写使能(w_en)有效,则w_addr[4:0]加1;否则不变。

//write address genaration

module w_addr_gen(clk,rst,wen,w_addr,full);

input clk,rst,wen,full;

output [:]w_addr;

reg [:]w_addr;

always @(posedge clk) //negedge rst can be here to make it asynchronous

begin

if (!rst) begin w_addr<='b00000; end

else if(wen==&&full==) begin w_addr<=w_addr+;end

else begin w_addr<='b00000; end

end

endmodule

Part 7.空满标志产生块:

flag_gen模块产生FIFO空满标志。本模块设计并不用读写地址判定FIFO是否空满。设计一个计数器,该计数器(pt_cnt)用于指示当前周期中FIFO中数据的个数。由于FIFO中最多只有16个数据,因此采用5位计数器来指示FIFO中数据个数。具体计算如下:

1)复位的时候,count=0;

2)如果w_en和r_en同时有效的时候,count不加也不减;表示同时对FIFO进行读写操作的时候,FIFO中的数据个数不变。

3)如果w_en有效且full=0,则count+1;表示写操作且FIFO未满时候,FIFO中的数据个数增加了1;

4)如果r_en有效且empty=0,则count-1; 表示读操作且FIFO未满时候,FIFO中的数据个数减少了1;

5)如果count=0的时候,表示FIFO空,需要设置empty=1;如果count=16的时候,表示FIFO现在已经满,需要设置full=1。

//empty and full flag gennaration

module flag_gen(clk,rst,ren,wen,empty,full);

input clk,ren,wen,rst;

output empty,full;

reg empty,full;

reg [:]count;

parameter max='b01111; always @(posedge clk)

begin

if(!rst) begin count<=;end

else case({ren,wen})

'b00: count<=count;

'b01: if(count!=max) count<=count+1;

'b10: if(count!=5'b0)count<=count-;

'b11: count<=count;

default:count<=count;

endcase

end always @(count)

begin

if (count==max) full<=;

else full<=;

end always @(count)

begin

if (count=='b0) empty<=1;

else empty<=;

end

endmodule

Verilog学习笔记简单功能实现(八)...............同步FIFO的更多相关文章

- Verilog学习笔记简单功能实现(三)...............同步有限状态机

在Verilog中可以采用多种方法来描述有限状态机最常见的方法就是用always和case语句.如下图所示的状态转移图就表示了一个简单的有限状态机: 图中:图表示了一个四状态的状态机,输入为A和Res ...

- Verilog学习笔记简单功能实现(八)...............异步FIFO

基本原理: 1.读写指针的工作原理 写指针:总是指向下一个将要被写入的单元,复位时,指向第1个单元(编号为0). 读指针:总是指向当前要被读出的数据,复位时,指向第1个单元(编号为0). ...

- Verilog学习笔记简单功能实现(二)...............全加器

先以一位全加器为例:Xi.Yi代表两个加数,Cin是地位进位信号,Cout是向高位的进位信号.列表有: Xi Yi Cin Sum Cout 0 0 0 0 0 0 0 1 1 0 ...

- Verilog学习笔记简单功能实现(六)...............计数分频电路

在分频器电路中最重要的概念有两个:1)奇分频/偶分频:2)占空比. A)其中最简单的就是二分频电路,占空比为50%,其Verilog程序为 module half_clk(clr,clk_in,clk ...

- Verilog学习笔记简单功能实现(五)...............序列检测设计

这里采用夏宇闻教授第十五章的序列检测为例来学习; 从以上的状态转换图可以写出状态机的程序: module seqdet(x,out,clk,rst); input x,clk,rst; output ...

- Verilog学习笔记简单功能实现(一)...............D触发器

module D_flop(data,clk,clr,q,qb); input data,clk,clr; output q,qb; wire a,b,c,d,e,f,ndata,nclk; nand ...

- Verilog学习笔记简单功能实现(四)...............译码器和编码器

这里以简单的3-8译码器和8-3编码器为例: module decoder3_8(a,out); :]a; :]out; 'b1<<a;/*把最低位的1左移in位(根据in口输入的值)并赋 ...

- Verilog学习笔记简单功能实现(七)...............接口设计(并行输入串行输出)

利用状态机实现比较复杂的接口设计: 这是一个将并行数据转换为串行输出的变换器,利用双向总线输出.这是由EEPROM读写器的缩减得到的,首先对I2C总线特征介绍: I2C总线(inter integra ...

- IIC驱动学习笔记,简单的TSC2007的IIC驱动编写,测试

IIC驱动学习笔记,简单的TSC2007的IIC驱动编写,测试 目的不是为了编写TSC2007驱动,是为了学习IIC驱动的编写,读一下TSC2007的ADC数据进行练习,, Linux主机驱动和外设驱 ...

随机推荐

- DOM对象 与 jQuery对象 之间的相互装换

示例代码: //jQuery对象转DOM对象 //因为jQuery对象是一个数组对象,所以转换为DOM对象时要用索引的形式 var $div1 = $("#div1"); //jQ ...

- javascript原型对象prototype

“我们创建的每一个函数都有一个prototype(原型)属性,这个属性是一个指针,指向一个对象,而这个对象的用途是包含可以由特定类型的所有实例共享的属性和方法.” 引用类型才具有prototype属性 ...

- CCNA网络工程师学习进程(6)vlan相关协议的配置与路由器简单配置介绍

前面已经介绍了大部分与vlan技术相关的交换机的协议的配置,更深层次的还有STP协议和以太网端口聚合技术,接着还会简单介绍一下路由器的基本应用. (1)STP(Spanning-tre ...

- Spring注意事项(各部分理解)

(1),每一个bean属性,就是一个普通的java类. 类有属性,有方法,如何交给容器管理.(注解的方式,xml方式配置) (2),通过Bean来实例化对象的方式 1.通过构造器(一般是无参的默认构造 ...

- C# List.ForEach 方法

C#中List.ForEach 方法是对 List 的每个元素执行指定操作. 示例: using System; using System.Collections.Generic; using Sys ...

- HTML的16个全局属性

前面的话 在HTML中,属性能表达相当丰富的语义,而且属性也会额外提供很多实用的功能,HTML共支持16个常见的全局属性. HTML原有属性 accesskey 作用:浏览器用来创建激活或聚焦元素的快 ...

- mysql 命令重命名表RENAME TABLE 句法

mysql 命令重命名表RENAME TABLE 句法 RENAME TABLE tbl_name TO new_tbl_name[, tbl_name2 TO new_tbl_name2,...]更 ...

- Spring MVC 学习总结(五)——校验与文件上传

Spring MVC不仅是在架构上改变了项目,使代码变得可复用.可维护与可扩展,其实在功能上也加强了不少. 验证与文件上传是许多项目中不可缺少的一部分.在项目中验证非常重要,首先是安全性考虑,如防止注 ...

- jQuery判断当前元素显示状态并控制元素的显示与隐藏

1.jQuery判断一个元素当前状态是显示还是隐藏 $("#id").is(':visible'); //true为显示,false为隐藏 $("#id") ...

- Java实时读取日志文件

古怪的需求 在实习的公司碰到一个古怪的需求:在一台服务器上写日志文件,每当日志文件写到一定大小时,比如是1G,会将这个日志文件改名成另一个名字,并新建一个与原文件名相同的日志文件,再往这个新建的日志文 ...